模块串联设计:

https://thedatabus.io/accelerator

cov + relu + pool

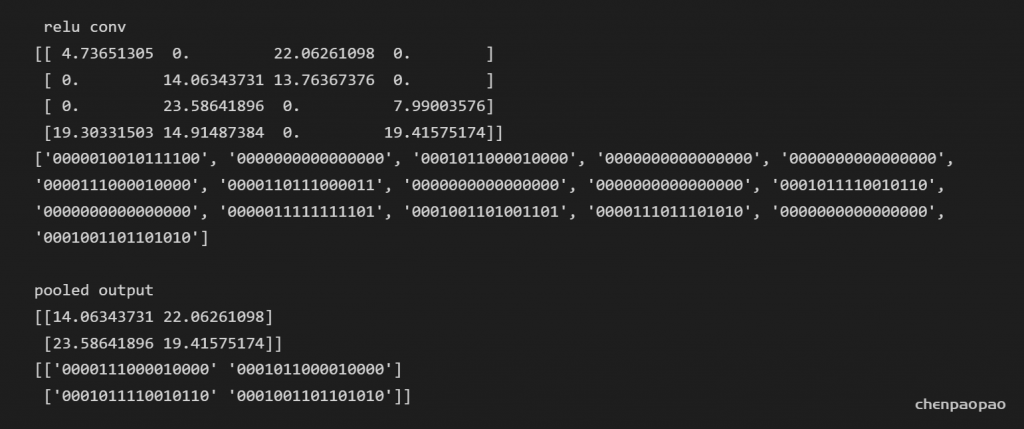

软件测试:

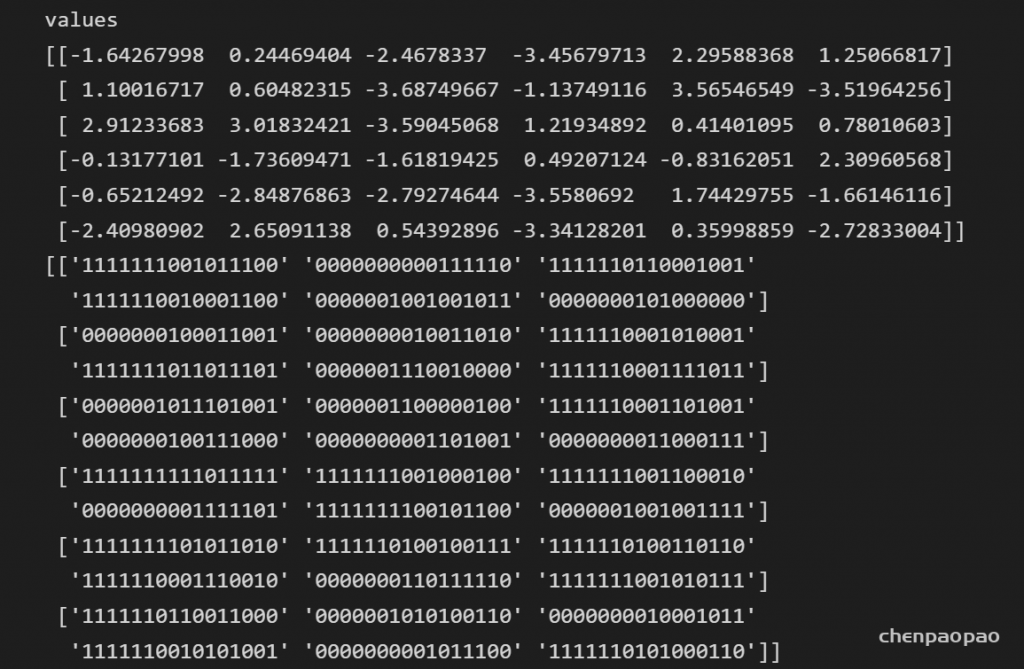

img:6*6

转浮点数:16bit :1符号位 7bit整数 8bit小数

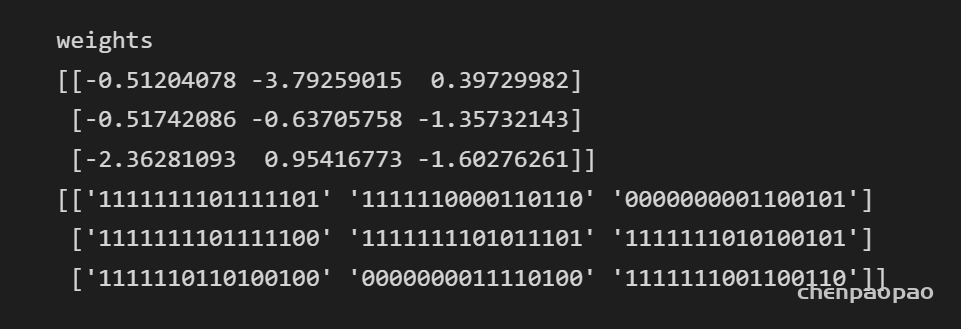

权重:

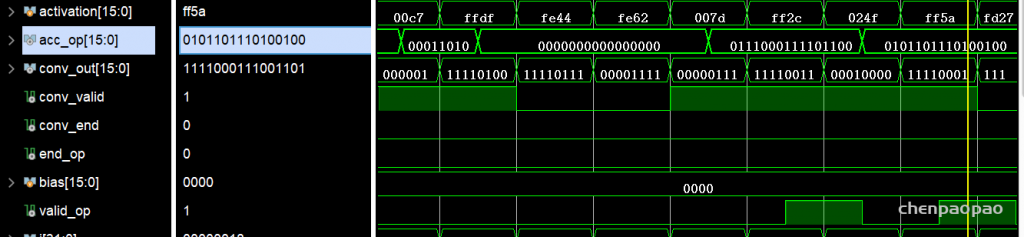

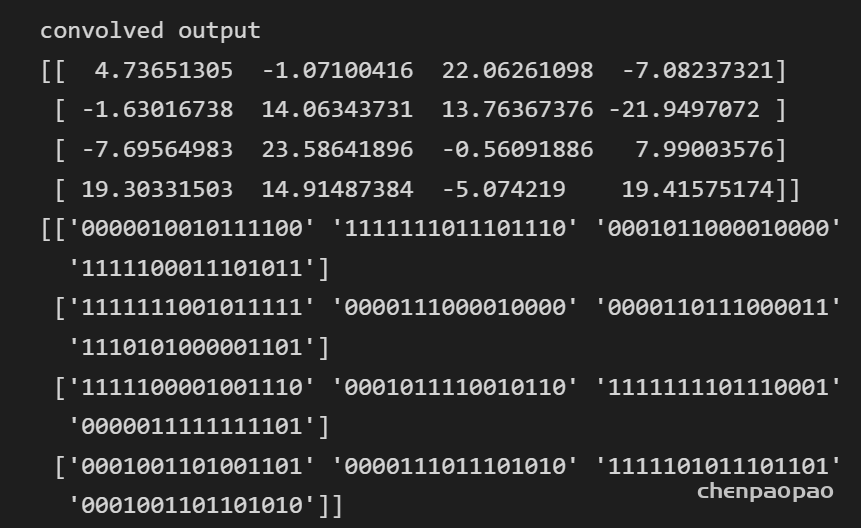

convolved output:

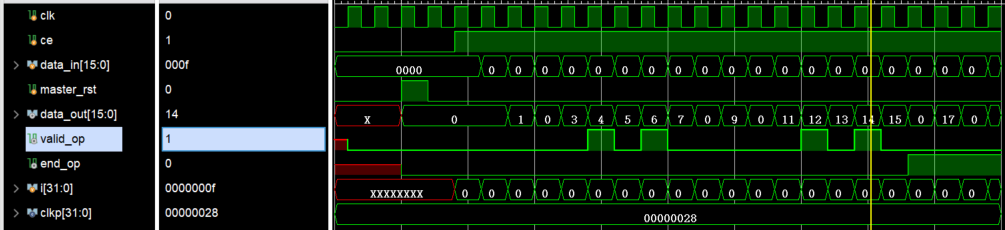

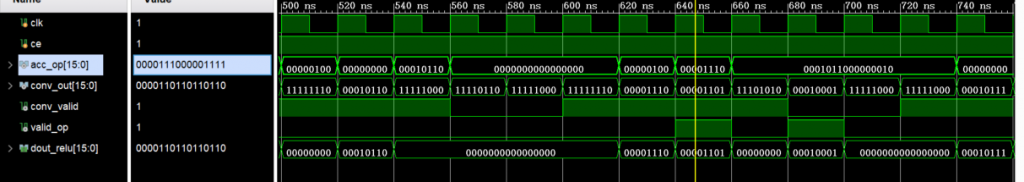

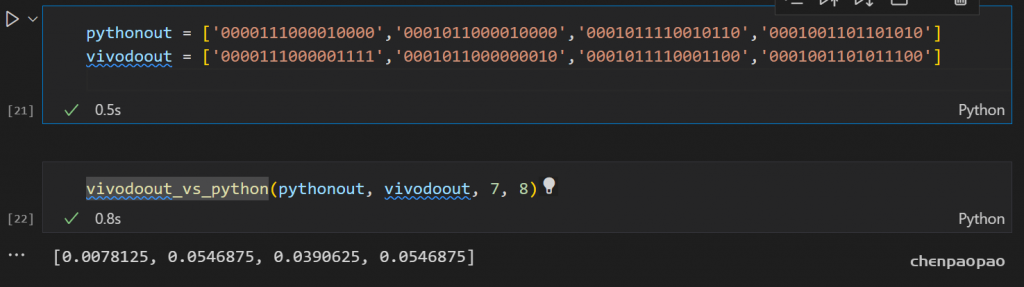

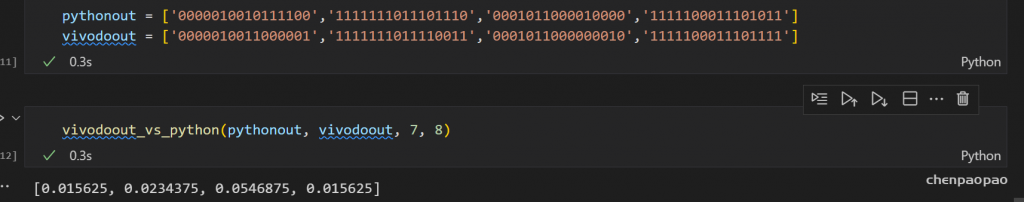

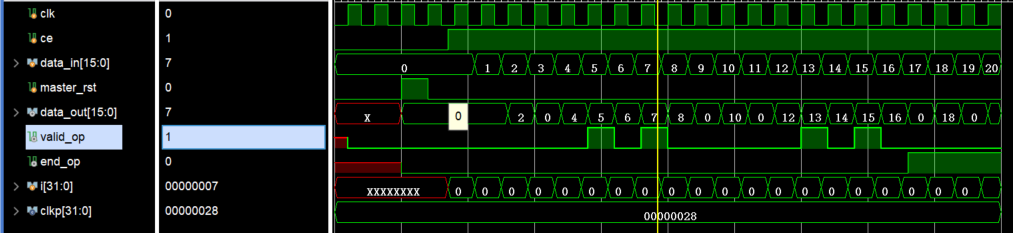

硬件仿真:(1,7,8)

可以发现软件和 vivado中error误差在 0.01量级

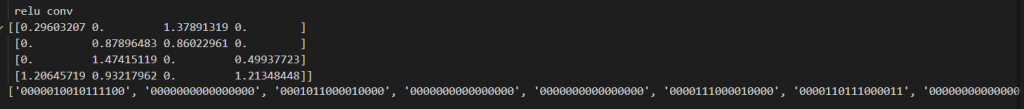

relu部分:

池化部分: (4*4矩阵) 2*2的池化

bug:

总会晚一个时钟计数:

+-----------+

|00|01|02|03|

+-----------+

|04|05|06|07|

+-----------+

|08|09|10|11|

+-----------+

|12|13|14|15|

+-----------+顺序输入 0,1,2,3,4,5,6,…

正确的应该是:

但如果对齐 ce和clk上升沿: