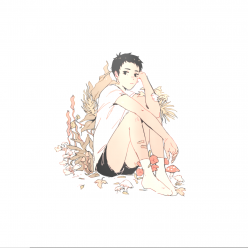

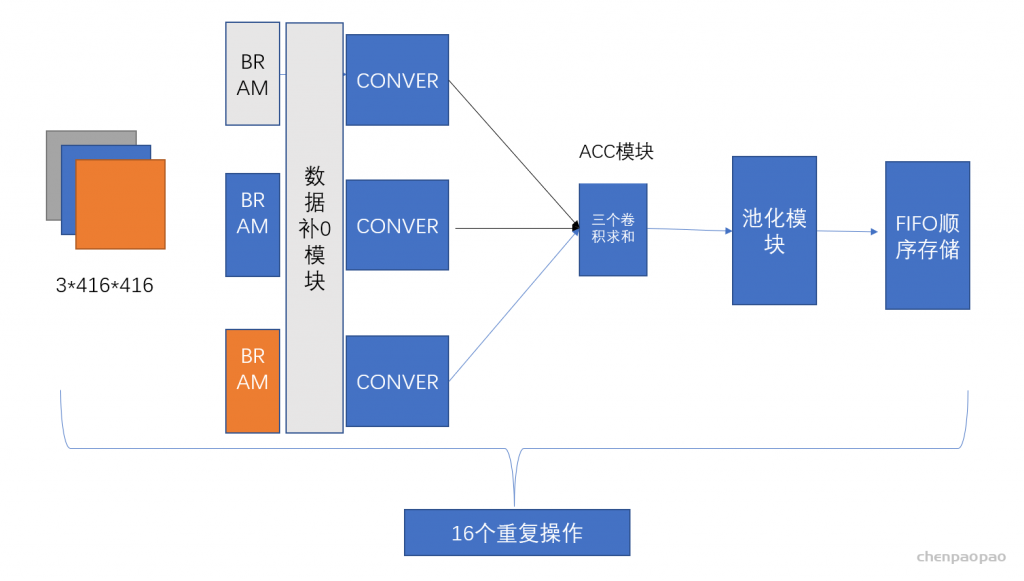

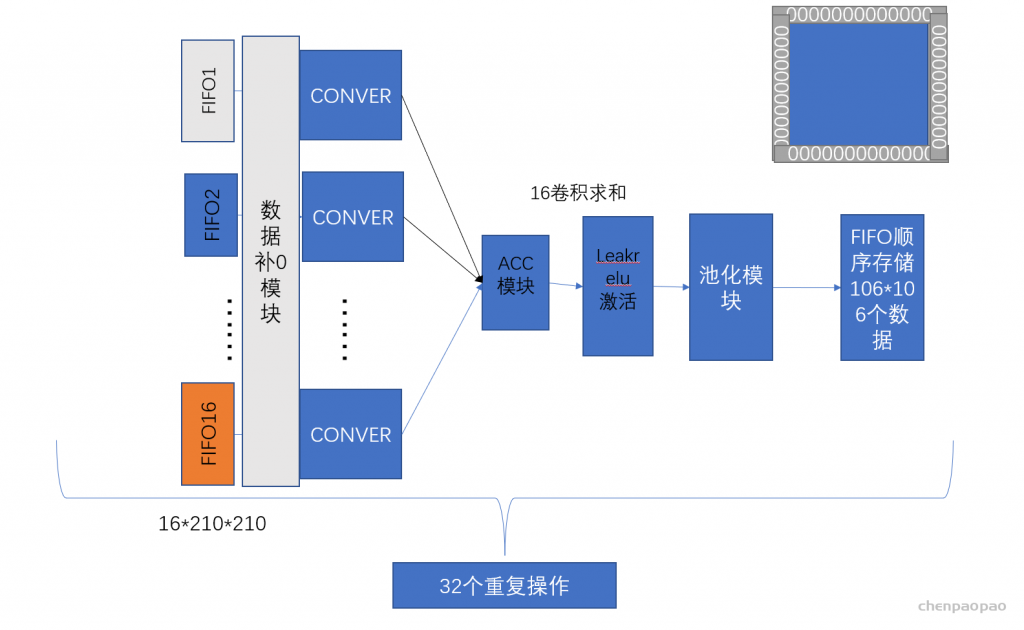

第N层的实现:

输入层:

第二层的实现:

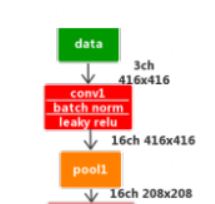

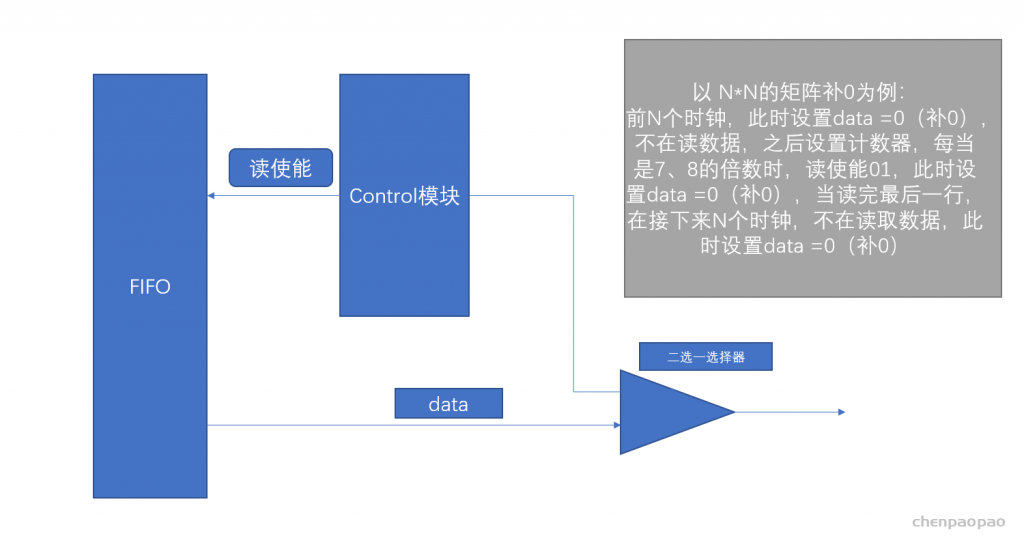

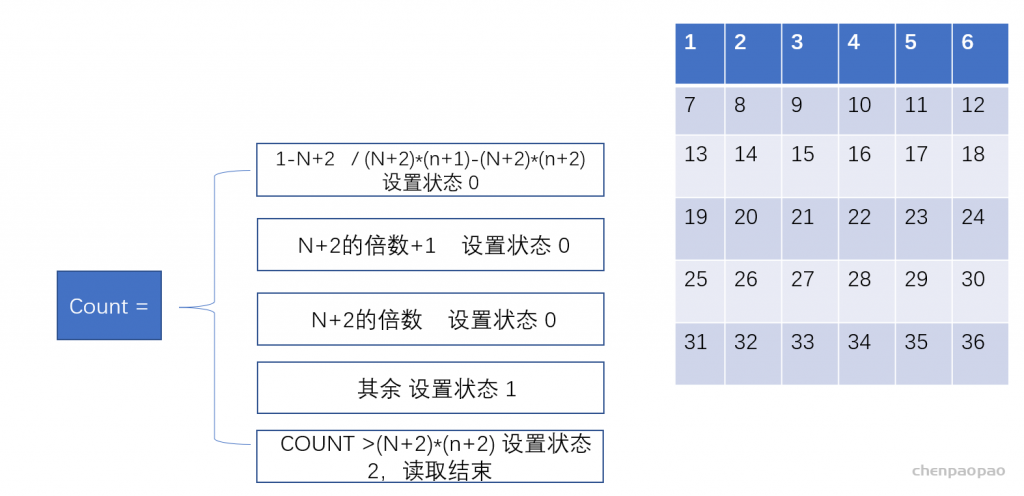

数据补0模块实现:

设置 计数器 :

module pad_fifo(

clk,ce,global_rst,pad_valid

);

parameter pad = 1;

parameter n = 9'h00a; //

input clk,ce,global_rst;

output reg pad_valid;

reg [31:0] count;

always@(posedge clk)begin

if(global_rst)begin

pad_valid <= 1'b0;

count<=0;

end

else if(count <= n+2*pad-1)begin

pad_valid <= 1'b1;

end

else if((count+1)%(n+2*pad)==1 || (count+1)%(n+2*pad)==0)begin

pad_valid <= 1'b1;

end

else if(count >= (n+2*pad)*(n+2*pad)-1)begin

pad_valid <= 1'b1;

end

else begin

pad_valid <= 1'b0;

end

end

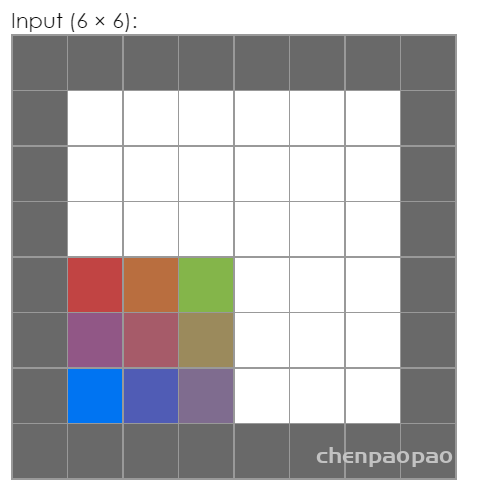

endmodule数据补0:对于yolo来说,还有一个池化层,需要对数据进行右下补0