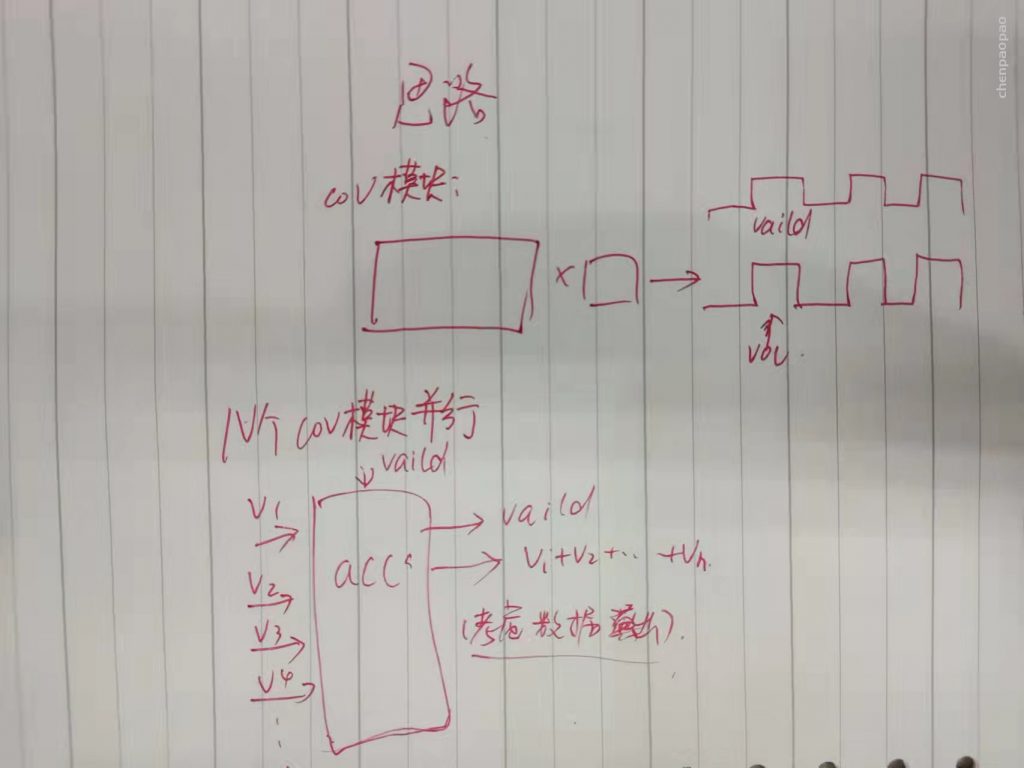

Acc累加模块

关键:

wire outconv [0:N*k*k-1];

reg [16:0] presum;

wire [16:0] cout;

generate

genvar l;

for(l=0;l<k*k;l=l+1)

begin

convolver #(9'h004,9'h003,1) uut (

.clk(clk),

.ce(ce),

.weight1(weight1),

.global_rst(global_rst),

.activation(activation),

.conv_op(outconv[N*l +: N]),

.end_conv(end_conv),

.valid_conv(valid_conv)

);

fadd ui(.a(outconv[N*l +: N]), //this i of ui won't be replaced

.b(mid),

.cout(cout),

);

end

assign mid = cout;

endgenerate

module fadd(

input [15:0] a, [15:0] b;

output [16:0] cout);

assign cout = a+b;