ZYNQ将高性能ARM Cotex-A系列处理器与高性能FPGA在单芯片内紧密结合,为设计带来了如减小体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与FPGA融合在一个芯片上之后,片内处理器与FPGA之间的互联通路就成了ZYNQ芯片设计的重中之重。如果Cotex-A9与FPGA之间的数据交互成为瓶颈,那么处理器与FPGA结合的性能优势就不能发挥出来。

AXI的英文全称是Advanced eXtensible Interface,即高级可扩展接口,它是ARM公司所提出的AMBA(Advanced Microcontroller Bus Architecture)协议的一部分

AXI协议就是描述主设备和从设备之间的数据传输方式,在该协议中,主设备和从设备之间通过握手信号建立连接。

AXI协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显着传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数0和1,因此可能需要一组信号才能高效地传输信息,这一组信号就组成了接口。AXI4协议支持以下三种类型的接口:

1、 AXI4:高性能存储映射接口。

2、 AXI4-Lite:简化版的AXI4接口,用于较少数据量的存储映射通信。

3、 AXI4-Stream:用于高速数据流传输,非存储映射接口。

在这里我们首先解释一下存储映射(Meamory Map)这一概念。如果一个协议是存储映射的,那么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表明是针对该存储空间的读写操作。

AXI4协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而AXI-Stream接口则像FIFO一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA接口等需要高速数据传输的场合。

AXI4:高性能存储映射接口

AXI4接口,它由五个独立的通道构成

1、 读地址

2、 读数据

3、 写地址

4、 写数据

5、 写响应

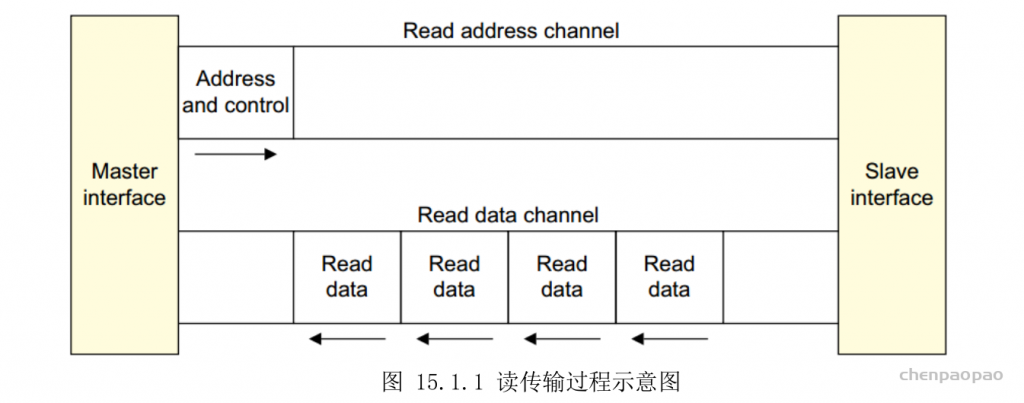

下面是使用读地址和读数据通道实现读传输过程的示意图:

从图 15.1.1中可以看到,在一个读传输过程中,主机首先在读地址通道给出读地址和控制信号,然后从机由读数据通道返回读出的数据。另外我们需要注意的是,这是一次突发读操作,主机只给出一个地址,从该地址连续突发读出四个数据。

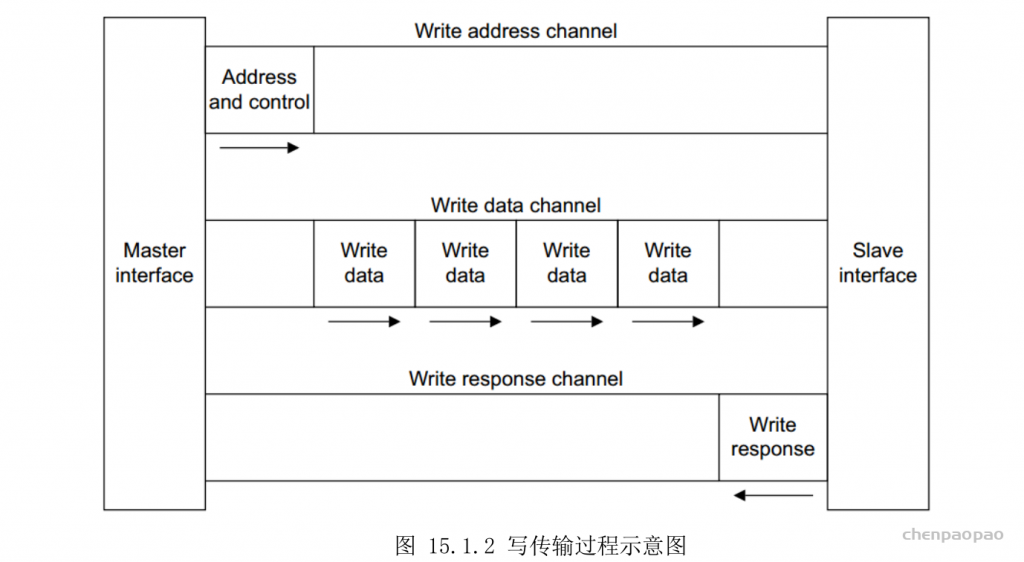

写传输过程如图 15.1.2所示,它用到了写地址、写数据和写响应三个通道。主机在写地址通道给出写地址和控制信号,然后在写数据通道连续突发写四个数据。从机在接收数据之后,在写响应通道给出响应信号。

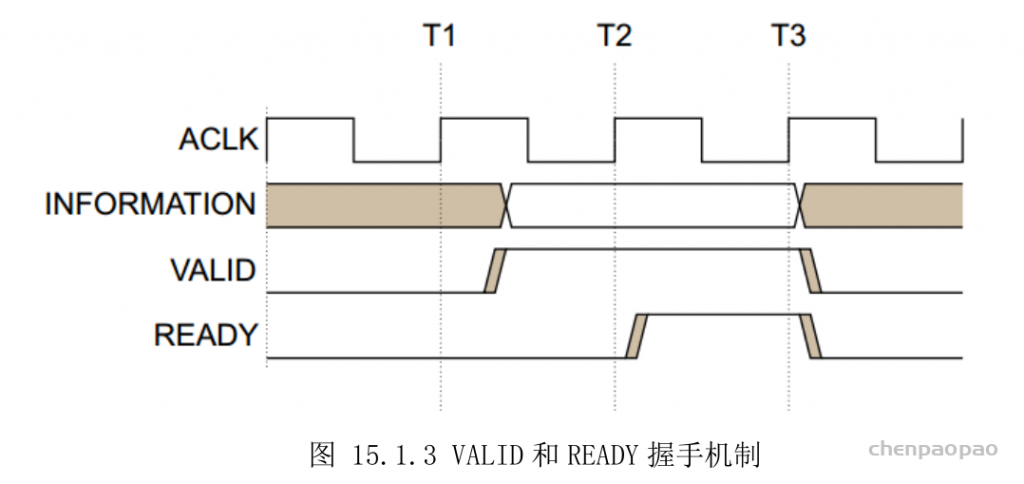

AXI总线中的每个通道都包含了一组信息信号,还有一个V ALID和一个READY信号。V ALID信号由源端(source)产生,表示当前地址或者数据线上的信息是有效的;而READY信号由目的端(destination)产生,则表示已经准备好接收地址、数据以及控制信息。VALID和READY信号提供了AXI总线中的握手机制,如下图所示:

ACLK为时钟信号,在AXI协议中,所有的输入信号都在是ACLK的上升沿采样,所

有的输出信号必须在ACLK的上升沿之后才能改变。在T1之后,源端将V ALID拉高,表明INFORMA TION信号线上传输的是有效的地址、数据或者控制信息。目的端在T2之后将READY拉高,表明它已经准备好接收数据,此时源端必须保持INFORMA TION数据稳定不变,直到T3时刻进行数据传输。

需要注意的是,源端不允许等目的端的READY信号拉高之后,才将V ALID信号置为有效状态。而且,一旦V ALID拉高,源端必须保持其处于有效状态,直至成功握手(在时钟上升沿检测到V ALID和READY同时为有效状态)。

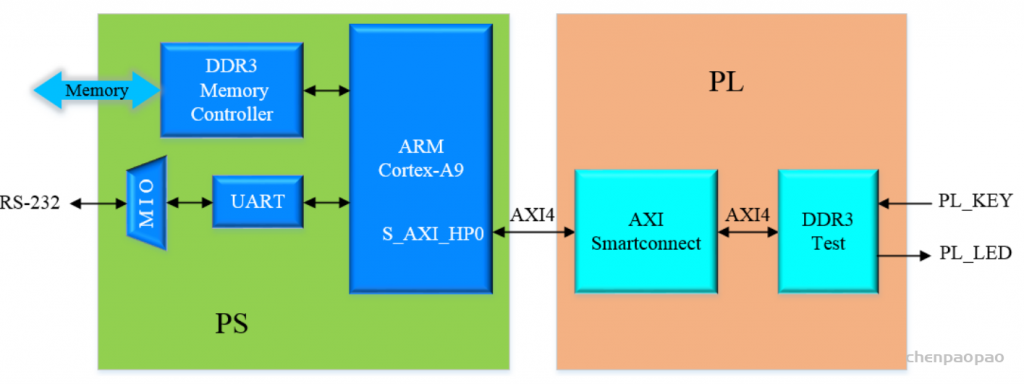

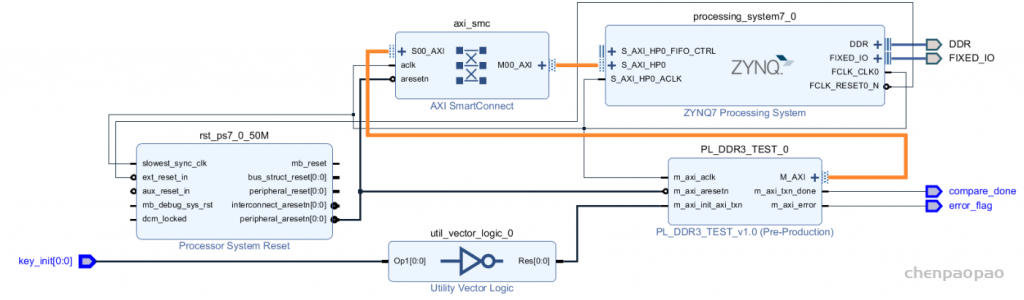

接下来通过自定义一个AXI4接口的IP核,通过AXI_HP接口对PS端DDR3进行读写测试。

我们在PL内自定义的DDR3 Test IP核作为主设备,通过PS AXI_HP0接口,与DDR控制器进行通信,最终对DDR3存储器进行读写操作。

SDK

1 #include <stdio.h>

2 #include "xil_cache.h"

3 #include "xil_printf.h"

4 #include "xil_io.h"

5

6 int main)()

7 {

8 int i;

9 char c;

10

11 Xil_DCacheDisable)();

12 print("AXI4 PL DDR TEST!\n\r";);

13

14 hlwhile(1{){

15 scanf("%c"&,&c;);

16 fif(c==='c'{){

17 printf("start\n\r";);

18 ofor(i=0;i<4096;i=i+4{){

19 printf("%d is %d\n",i(,(int)Xil_In32(0x10000000+i)));

20 }

21 }

22 }

23

24 eunreturn 0;

25 } AXI4-Stream协议

AXI4-Stream协议一般被翻译为AXI流协议,是AXI总线的一种演化版本。AXI4流协议作为一个标准接口,用于连接进行数据交换的组件。接口可以用来连接一个单一的主机,主机向接收数据的单一从机发送数据,也可用于连接若干个主机和从机的组件。协议支持共用一组信号线的多个数据流,允许构建一个通用互联。相比于AHB/APB,AXI流协议提出了数据包、数据帧以及传输操作等概念,这也是其被称为流(Stream)的原因。

关于AXI Stream的基本概念解释如下:

传输(Transfer):通过 AXI4 流接口进行的一个单一数据传输。一个单一数据传输由TV ALID和TREADY握手信号定义。

包(Packet):通过 AXI4 流接口被一起传输的一组字节,包类似于 AXI4 的突发。

帧(Frame):一个 AXI4 流中最高级别的字节编组。一帧可以包含很大数量的字节数,例如,一个完整的视频帧缓存。

数据流(Data Stream):从一个源设备到一个目标设备传输的数据。

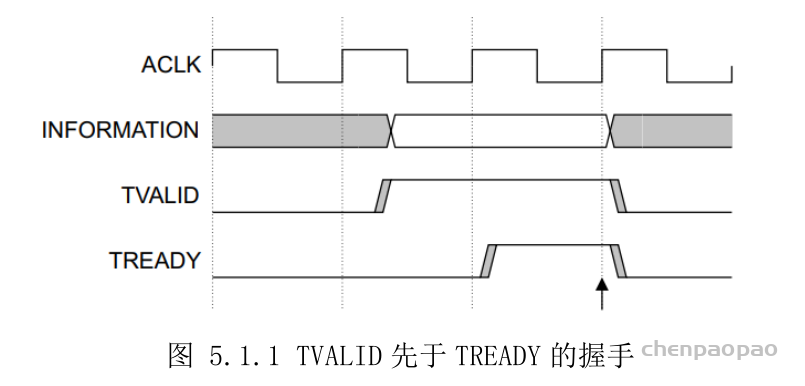

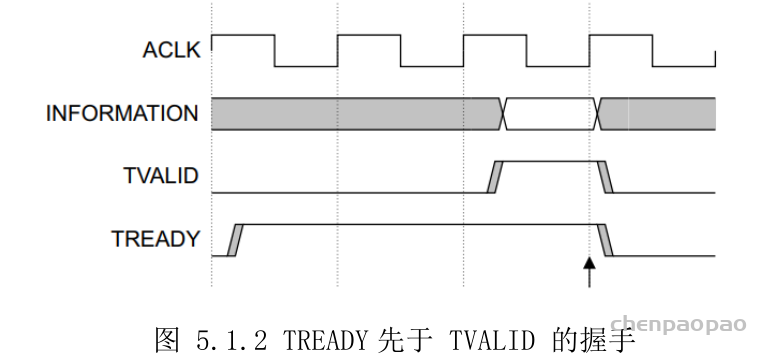

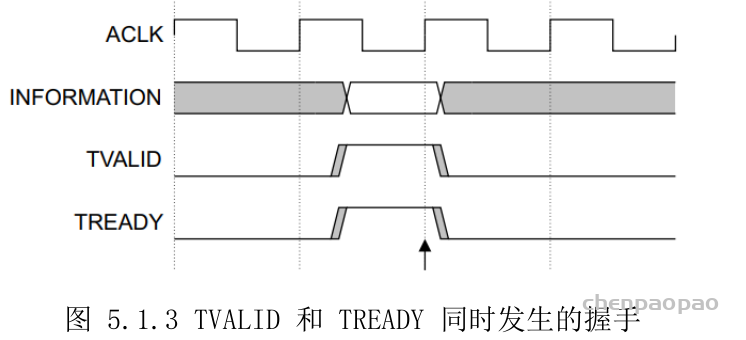

两个模块之间进行数据传输,需要事先约定好这两个模块之间的传输协议,这是两个信号握手的概念。TV ALID和TREADY信号的握手包含三种情况:TV ALID先于 TREADY 的握手、TREADY先于 TV ALID的握手、TV ALID 和 TREADY 同时发生的握手。

注意该协议中使用上升沿采样

下图中,主机发出了数据和控制信息并将TV ALID 信号置为高。一旦主机驱动了 TV ALID ,主机发出的数据或控制信息必须保持不变,直到从机驱动 TREADY 信号为高表示可以接收数据和控制信息。在这种情况下,一旦从机设置 TREADY 为高,传输就会发生。箭头标示出了传输发生的位置。

下图中,从机在数据和控制信息有效之前驱动TREADY为高。这表示目标设备可以在一个ACLK周期内接收数据和控制信息。在这种情况下,一旦主机驱动 TV ALID 为高,则传输就会发生。箭头标示出了传输发生的位置。

下图中,主机驱动TV ALID为高,从机在同一时钟(ACLK)周期内也驱动TREADY为高。在这种情况下,如图中箭头标注,传输在同一周期内发生。

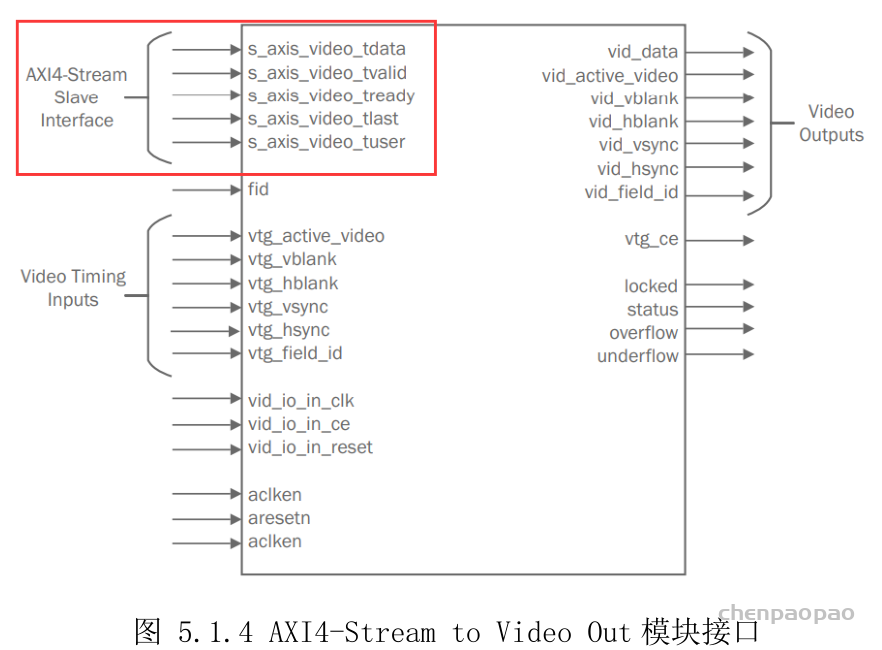

本次实验我们需要使用Vivado HLS工具生成带有AXI4-Stream接口的IP核,并将此IP核的AXI4-Stream接口连接到“AXI4-Stream to Video Out”模块中的AXI4-Stream接口,如下图所示:

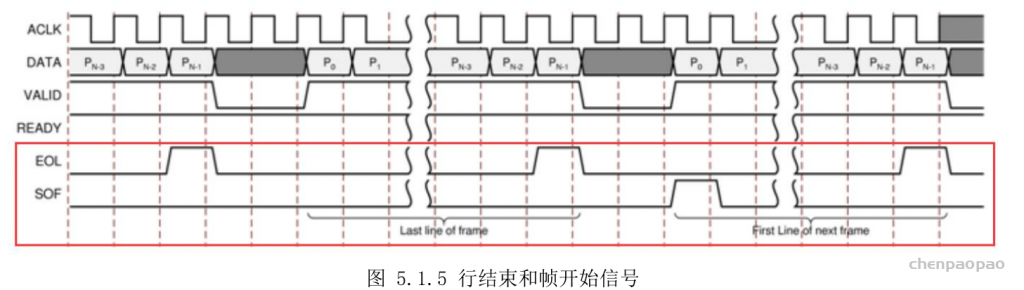

我们重点关注图中的“s_axis_video_tlast”和“s_axis_video_tuser” 信号,其中“s_axis_video_tlast”是AXI4-Stream协议中“TLAST”信号,这个信号设置为高表示一行像素传输结束,“s_axis_video_tuser”是AXI4-Stream协议中的“TUSER”信号,这个信号设置为高表示一帧图像传输开始。时序图如下图所示:

图中的“EOL”表示“End of line”是行传输结束信号,它在一行图像像素传输结束的时候拉高一个时钟周期;图中的“SOF”表示“Start of frame”是帧传输开始信号。它在一帧图像像素传输开始的时候拉高一个时钟周期。